The semiconductor industry presents a peculiar challenge: a high-stakes marathon where a single “bug” in a chip, a tiny misstep among millions of transistors, can lead to multi-million dollar prototypes failing to “boot” and, for smaller entities, even bankruptcy. This inherent risk aversion necessitates months of exhaustive verification, a testament to the industry’s deep-seated paranoia for functional integrity. Indeed, establishing an Intellectual Property (IP) company in this domain is often considered “the worst idea you could have,” given the immense upfront investment and the protracted, uncertain path to returns.

Yet, success in this computationally intensive frontier hinges on a few critical “algorithms” for survival and dominance:

• Embracing Open Standards: The RISC-V Opportunity. Proprietary Instruction Set Architectures (ISAs) have historically imposed monopolies, stifling innovation. RISC-V, an open-standard ISA, is not merely a technical specification but an “open opportunity”—a strategic liberation. Unlike copyleft licenses, RISC-V allows for unfettered use, customization, and commercialization, democratizing access to the fundamental language between hardware and software. India’s early adoption, through institutions like IIT Madras, signifies a deliberate move to control the entire “loop from specification to production,” a critical component for national security and tailored solutions. The fact that Nvidia shipped over a billion RISC-V parts in 2024 speaks to its accelerating global adoption.

• Beyond the Core: The “Campus” Imperative. A chip’s computational “core” is merely the “admin building” of a complex entity. Customers demand comprehensive “solutions,” encompassing entire “campuses” of integrated components: subsystems, Systems-on-Chip (SoCs), peripherals (USB, Wi-Fi), memory, accelerators, security modules, and interconnects. A successful semiconductor business must provide this full functional organism, as “the core alone does not sell.”

• Accelerating the Design “Metabolism”: From Months to Days. Traditionally, the entire chip product development cycle spans 12-18 months, with the initial design phase (spec-to-RTL freeze) consuming at least four. This serialized process is an evolutionary bottleneck. The answer lies in “generator platforms.” These are not passive tools but active “design engines” that collapse the iteration cycle to weeks or even days. This rapid feedback loop enables swift optimization across the critical dimensions of PPA (Power, Performance, Area)—minimizing energy consumption, maximizing computational speed, and shrinking physical silicon footprint, all directly impacting cost and market viability. This shift parallels the software industry’s evolution from monolithic releases to continuous integration, allowing innovators to focus on their unique contributions (e.g., an AI accelerator) rather than mundane components.

• AI as “Co-Pilot,” Not “Designer God.” While AI serves as a powerful “co-pilot,” particularly in verification and identifying complex “corner cases,” it is not yet capable of autonomous chip design. The industry’s extreme risk aversion, the dearth of open-source training data, and the inherent issues of “hallucinations” and reproducibility prevent full reliance on AI for core design. Chip designers anticipate “ruling for quite some decades” before AI supplants their cognitive labor, though AI can effectively interface with existing generation tools.

The entrepreneurial journey in this space is equally a process of adaptation:

• “Sell Before You Build”: The Market’s Imperative. The academic pursuit of “what’s possible” must yield to the entrepreneurial demand for “what’s needed” and “what’s sellable.” This often means “throwing it over the wall”—sampling imperfect products with customers, overcoming the deep-seated “fear of failure.” Securing the “first customer” is the most formidable hurdle, requiring immense flexibility and commitment, as they represent the crucial “silicon proof” and “market proof” that validates a startup’s viability.

• Navigating the Multi-Agent Ecosystem. A founder is perpetually “selling”—to employees, investors, and customers. This requires a nuanced understanding of divergent expectations, whether from long-term capital providers or government initiatives (like India’s Design Linked Incentive scheme, which dramatically offsets tooling costs). Strategic “calls” must be made when customer demands diverge from other stakeholder priorities.

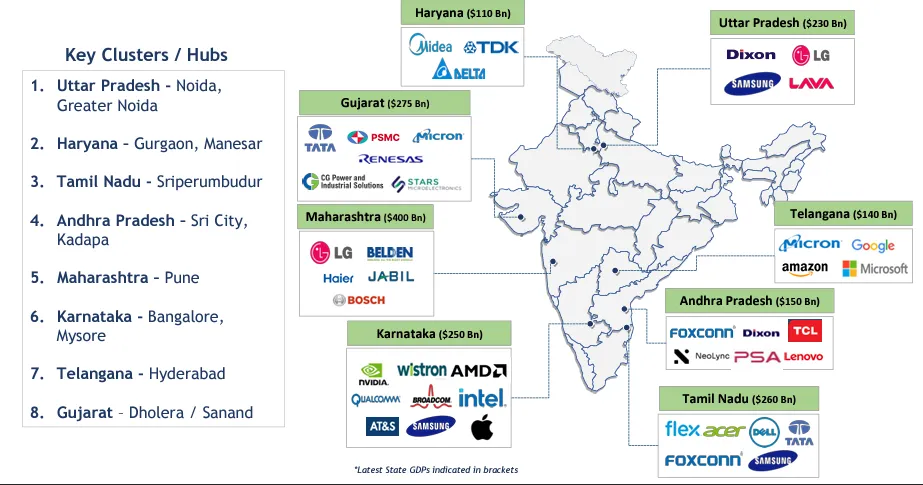

• Global Scalability and India’s “Waves.” Semiconductor IP is inherently globally scalable. Once initial customers validate the product, sales cycles drastically shorten. India’s semiconductor evolution is seen in two strategic “waves”: the first, focused on manufacturing to reduce electronics imports; the second, on building “smarter, automated designs and IPs”—innovating at the silicon level to address India’s unique problems and cultural contexts, ensuring indigenous control over the entire digital ecosystem.

Ultimately, cultivating the right mindset is paramount: overcoming the paralyzing “fear of failure,” embracing “patriotism” (evident in government support and a burgeoning willingness to “build in India”), and understanding that this industry demands “patient capital” and a long-term vision—a marathon, indeed, that determined engineers are striving to transform into a sprint.